购物车0

购物车0

描述:

该AT45DB321是一个只有2.7伏,串行接口闪存适合于-系TEM重新编程。它的34603008位的存储器被组织为8192页528字节每个。除了在主存储器中, AT45DB321还包含两个每528字节的SRAM数据缓冲区。该缓冲器允许接收而数据在主存储器页面进行重新编程。

特点:

1、单2.7V - 3.6V电源

2、串行接口架构

3、页编程操作

- 单周期重新编程(擦除和编程)

- 8192页( 528字节/页)主内存

4、可选页和块擦除操作

5、两个528字节的SRAM数据缓冲区 - 允许数据的接收,同时重新编程

非易失性存储器

6、内部的计划和控制的定时器

7、快速页编程时间 - 7毫秒典型

8、120 µš典型的页面,以缓冲传输时间

9、低功耗

- 4毫安有效的读电流典型

– 3µ一种CMOS待机电流典型

10、13 MHz的最大时钟频率

11、硬件数据保护功能

12、串行外设接口( SPI )兼容 - 模式0和3

13、CMOS和TTL兼容输入和输出

14、商用和工业温度范围

AT45DB321E-MWHF-T电路图

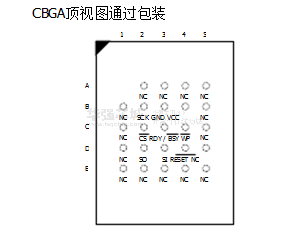

AT45DB321E-MWHF-T 引脚图

AT45DB321E-MWHF-T 引脚图

AT45DB321E-MWHF-T 引脚图

AT45DB321E-MWHF-T 封装图

AT45DB321E-MWHF-T 封装图

Flash存储器按其接口可分为串行和并行两大类。串行Flash存储器大多采用I2C接口或SPI接口进行读写;与并行Flash存储器相比,所需引脚少、体积小、易于扩展、与单片机或控制器连接简单、工作可靠,所以串行Flash存储器越来越多...

本文给出的是用于大型光伏系统运行状态监测的数据采集存储电路,由于采用表面贴片工艺制作,整个电路板的宽度仅为18毫米,就像使用U盘一样方便。

SN74AVC1T45设计用于两条数据总线之间的异步通信。方向控制(DIR)输入的逻辑电平激活B端口输出或A端口输出。

合作伙伴! E5062A主要指标: E5062A频率:300K-3G 欧姆 *T/R 或 S 参数综合测试仪 *50 或 75 欧姆测试端口阻抗 *120 dB 的动

本应用笔记是关于如何布局Maxim T3/E3线路接口单元(LIU)网络接口的指南。该指南以DS315x产品为例。本应用笔记也适用于其他Maxim T3/E3产品。

) 放掉的电能ΔE=E1-E2=45-5=40(焦耳) 假设以恒定功率P瓦放电,放电时间t=E/P=40/P(秒 fqj

本应用笔记提供了使用达拉斯半导体/Maxim通信产品T1/E1单芯片收发器(SCT)和T1/E1成帧器的小数T1和E1电路设计示例。

本应用笔记介绍如何使用达拉斯半导体DS21X52和DS21X54单芯片收发器(SCT)和DS216xx时钟适配器(CLAD)将T1转换为E1,反之亦然。DS21X52 SCT用于T1信号

| ADCMP564 | AT91SAM9263 | ad5791 | AD8128 |

| ADUC7020 | AD7262 | AD766 | ADUM3441 |

| ADN2525 | ADG407 | ADC12138 | AD976A |

| AT25M02 | ADSP-TS202S | ADG1312 | ADXL278 |

| AD9243 | ADL5721 | ADA4853-3 | ADM805 |