购物车0

购物车0制造商:ADI/AD

优势和特点

JESD204B (Subclass 1) coded serial digital outputs

Lane rates up to 16 Gbps

1.6 W total power at 1300 MSPS

800 mW per ADC channel

SNR = 65.6 dBFS at 172 MHz (1.59 V p-p input range)

SFDR = 78 dBFS at 172.3 MHz (1.59 V p-p input range)

Noise density

−153.9 dBFS/Hz (1.59 V p-p input range)

−155.6 dBFS/Hz (2.04 V p-p input range)

0.95 V, 1.8 V, and 2.5 V supply operation

No missing codes

Internal ADC voltage reference

Flexible input range

1.36 V p-p to 2.04 V p-p (1.59 V p-p typical)

2 GHz usable analog input full power bandwidth

>95 dB channel isolation/crosstalk

Amplitude detect bits for efficient AGC implementation

2 integrated digital downconverters per ADC channel

48-bit NCO

Programmable decimation rates

Differential clock input

SPI control

Integer clock divide by 2 and divide by 4

Flexible JESD204B lane configurations

On-chip dithering to improve small signal linerarity

产品详情

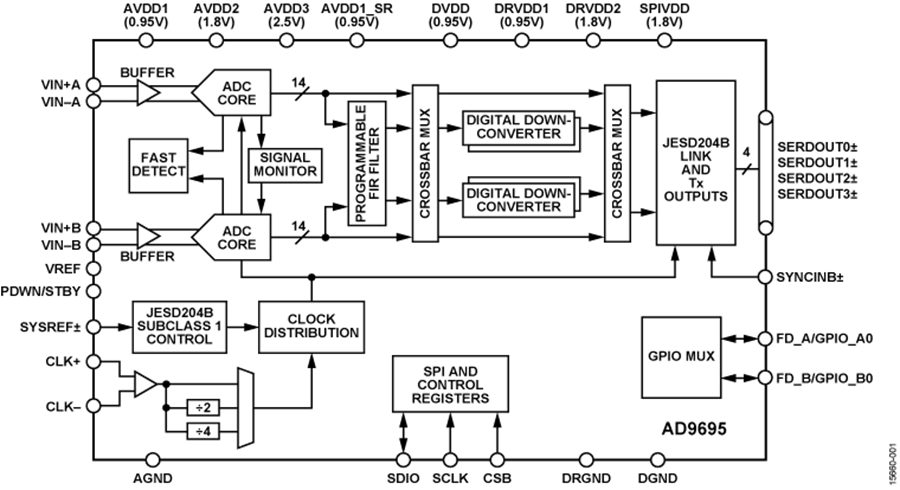

The AD9695 is a dual, 14-bit, 1300 MSPS/625 MSPS analog-todigitalconverter (ADC). The device has an on-chip buffer and asample-and-hold circuit designed for low power, small size, andease of use. This product is designed to support communicationsapplications capable of direct sampling wide bandwidth analogsignals of up to 2 GHz. The −3 dB bandwidth of the ADC inputis 2 GHz. The AD9695 is optimized for wide input bandwidth,high sampling rate, excellent linearity, and low power in a smallpackage.

The dual ADC cores feature a multistage, differential pipelinedarchitecture with integrated output error correction logic. EachADC features wide bandwidth inputs supporting a variety ofuser-selectable input ranges. An integrated voltage referenceeases design considerations. The analog input and clock signalsare differential inputs. The ADC data outputs are internallyconnected to four digital downconverters (DDCs) through acrossbar mux. Each DDC consists of multiple signal processingstages: a 48-bit frequency translator (numerically controlledoscillator (NCO)), and decimation filters. The NCO has the optionto select up to 16 preset bands over the general-purpose input/output (GPIO) pins, or use a coherent fast frequency hoppingmechanism for band selection. Operation of the AD9695 betweenthe DDC modes is selectable via SPI-programmable profiles.

In addition to the DDC blocks, the AD9695 has several functionsthat simplify the automatic gain control (AGC) function in acommunications receiver. The programmable threshold detectorallows monitoring of the incoming signal power using the fastdetect control bits in Register 0x0245 of the ADC. If the inputsignal level exceeds the programmable threshold, the fast detectindicator goes high. Because this threshold indicator has lowlatency, the user can quickly turn down the system gain to avoidan overrange condition at the ADC input. In addition to the fastdetect outputs, the AD9695 also offers signal monitoringcapability. The signal monitoring block provides additionalinformation about the signal being digitized by the ADC.

The user can configure the Subclasss 1 JESD204B-based highspeed serialized output using either one lane, two lanes, or fourlanes, depending on the DDC configuration and the acceptablelane rate of the receiving logic device. Multidevice synchronizationis supported through the SYSREF± and SYNCINB± input pins.The AD9695 has flexible power-down options that allowsignificant power savings when desired. All of these features canbe programmed using a 3-wire serial port interface (SPI) and orPDWN/STBY pin.

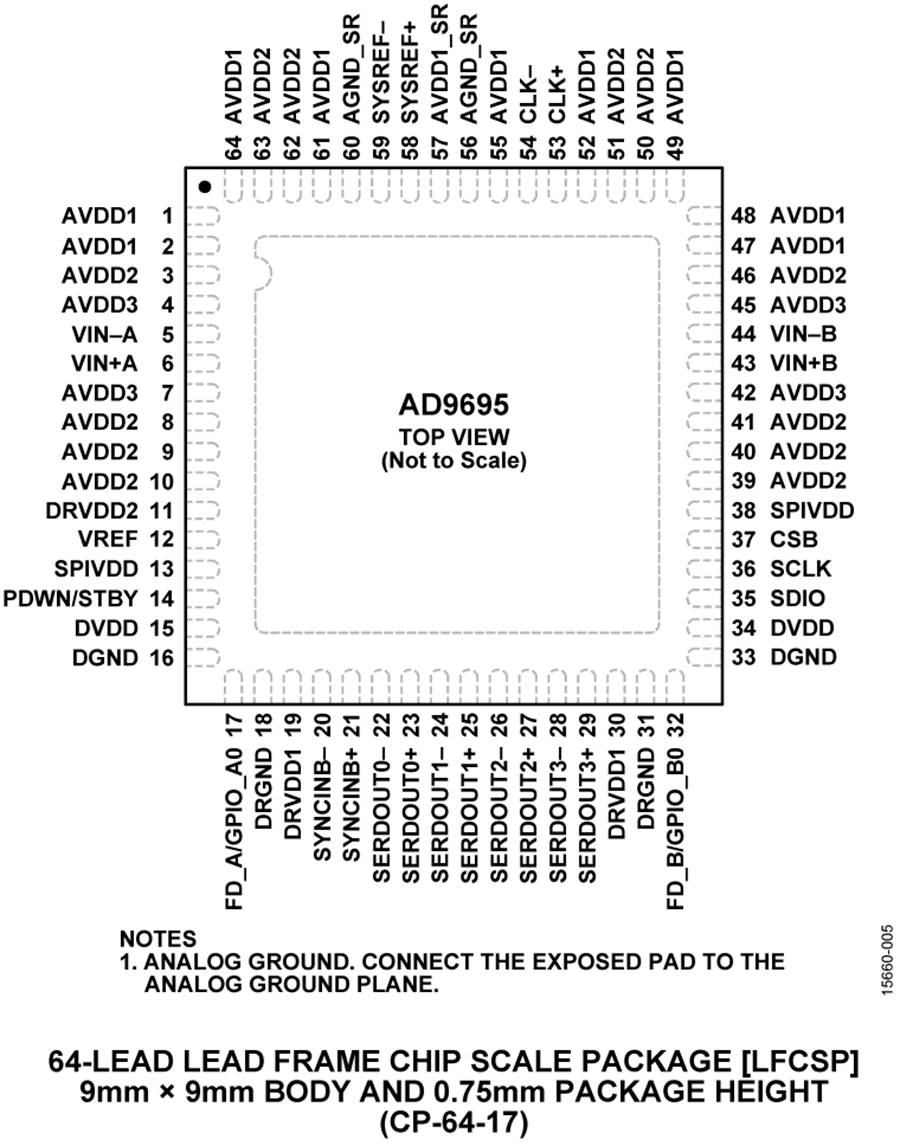

The AD9695 is available in a Pb-free, 64-lead LFCSP and isspecified over the −40°C to +105°C junction temperature range.This product may be protected by one or more U.S. orinternational patents.

Note that, throughout this data sheet, multifunction pins, suchas FD_A/GPIO_A0, are referred to either by the entire pinname or by a single function of the pin, for example, FD_A,when only that function is relevant.

Product Highlights

Low power consumption per channel.

JESD204B lane rate support up to 16 Gbps.

Wide, full power bandwidth supports intermediate

frequency (IF) sampling of signals up to 2 GHz.Buffered inputs ease filter design and implementation.

Four integrated wideband decimation filters and NCO

blocks supporting multiband receivers.Programmable fast overrange detection.

On-chip temperature diode for system thermal management.

Applications

Communications

Diversity multiband, multimode digital receivers

3G/4G, TD-SCDMA, WCDMA, GSM, LTE

General-purpose software radios

Ultrawideband satellite receiver

Instrumentation

Oscilloscopes

Spectrum analyzers

Network analyzers

Integrated RF test solutions

Radar

Electronic support measures, electronic counter measures, and electronic counter-counter measures

High speed data acquisition systems

DOCSIS 3.0 CMTS upstream receive paths

Hybrid fiber coaxial digital reverse path receivers

Wideband digital predistortion

AD9695 引脚图

AD9695电路图

| 型号 | 制造商 | 描述 | 购买 |

|---|---|---|---|

| AD9695BCPZRL7-625 | - | - | 立即购买 |

| AD9695BCPZRL7-1300 | - | - | 立即购买 |

| AD9695BCPZ-625 | - | - | 立即购买 |

| AD9695BCPZ-1300 | - | - | 立即购买 |

XSP01A快充协议芯片是一款集成USB Power Delivery(PD)2.0/3.0快充协议的USB-C/Type-C多功能取电芯片,支持从手机充电器/车充等电源上取电给产品供电,它具有广泛的兼容性,支持华为、苹果、三星、小米、倍思、OPPO等多家上百款PD协议充电器,支持取电5V、9V、12V、15V、20V。

意法半导体(ST)作为世界领先的半导体供应商,凭借多年的经验和先进的技术创新为客户提供解决方案。丰富的产品类别,涵盖汽车、工业、通信设备、计算机及外设以及个人电子终端市场。

在工业自动化与智能化日益普及的今天,传感器作为连接物理世界与数字世界的桥梁,扮演着举足轻重的角色。其中,槽型光电传感器以其独特的设计、高精度的检测能力以及广泛的应用场景,成为了工业自动化领域中的一颗璀璨明星。本文将深入探讨槽型光电传感器的创新应用及其卓越性能,揭示其在提升生产效率、保障产品质量方面的独特价值。

近日,上海见证了一场科技界的强强联合——行芯、EDA²与华为云共同宣布签署了一项具有深远影响的战略合作框架协议。此次合作标志着三方在EDA(电子设计自动化)评测领域迈出了坚实的一步,旨在通过优势互补,实现互利共赢的新局面。

超级电容器由于其独特的物理和化学特性,可以被串联使用以适应不同的电源需求。

作者:Damon Tarry, Design Applications Engineer, Same Sky 本 Arduino 示例代码教程旨在为用户提供一个坚实的起点,以便通过串行外设接口 (SPI) 通信来配置和读取 [Same Sky] 的 [AMT22 绝对编码器] 的数据。该教程将提供所需的硬件和软件、关键设置要求以及单圈和多圈输出选项的示例代码包和说明。以下是入门工作所需的物料清单: [Arduino 板] [AMT22 编码器] [AMT-06C-1-036 电缆] ,或带有相应连接器的类似电缆 [Arduino IDE] [下载 AMT22 单圈样例代码] [下载 AMT22 多圈样例代码]

# 【技术分享】远程透传网关-单网口快速实现汇川PLC-AutoShop程序远程上下载

在电动汽车(EV)动力总成中讨论更激烈的部件旁边是机电开关,称为接触器。尽管它们在引擎盖下平淡无奇,但它们是保持电动汽车平稳运行的功能和安全要素的一部分。鉴于 41 年电动汽车注册量增长了 2020%1,并且每辆车都有几个接触器,这确实是一个重要的组件部分。

| ADG5436 | AD8363 | AD526 | AD8302 |

| AD8274 | AD9601 | AT91SAM9G20 | AD9648 |

| AD7654 | ATA663254 | ADG774 | ADG5206 |

| ADM6823 | AD7228 | ASM3P2111B | ADG431 |

| ADM8690 | ADF7241 | ADP5042 | AD5144A |

元器件业务:

0731-85350837

0731-85351037

PCB/SMT/PCBA业务:

0755-83688678

周一至周五(9:00-12:00 13:30-18:30)节假日除外

投诉电话:19925199461

微信公众平台

搜索:hqchip001

型号搜索订单查询