0

0

电子产业一站式服务平台

电子百科

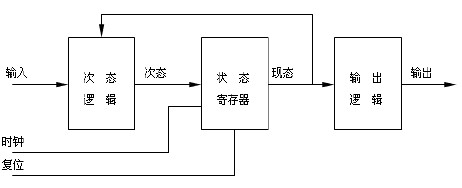

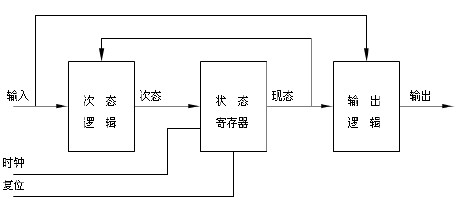

有限状态机由组合逻辑和寄存器逻辑组成。

1、寄存器逻辑的功能:用来存储有限状态机的内部状态。

2、组合逻辑又可以分为次态逻辑和输出逻辑两个部分。其中次态逻辑的功能是用来确定有限状态机的下一个状态;而输出逻辑就是用来确定有限状态机的输出。

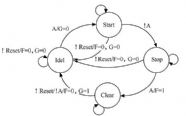

在实际的应用中,根据有限状态机是否使用输入信号,设计人员经常将其分为Moore型有限状态机和Mealy型有限状态机两种类型。

1、Moore型有限状态机:是指那些输出信号仅与当前状态有关的有限状态机,即可以把Moore型有限状态机的输出看成是当前状态的函数。

2、Mealy型有限状态机:是指那些输出信号不仅与当前状态有关,而且还与所有的输入信号有关的有限状态机,即可以把Mealy有限状态机的输出看成是当前状态和所有输入信号的函数。可见,Mealy有限状态机要比Moore型有限状态机复杂一些。

Moore型和Mealy型有限状态机的区别:Moore型有限状态机仅与当前状态有关,而与输入信号无关;Mealy型有限状态机不但与当前状态有关,而且还与状态机的输入信号有关。

有限状态机的描述规则:

1、至少包含一个状态信号,用来指状态;

2、状态转移指定和输出指定;

3、时钟信号,一般用来同步;

4、同步或者异步复位信号。

其中:第1条到第3条是必须包括的,而第4条则不是必须含有的。

有限状态机的描述方式有三进程、双进程和单进程描述方式。

1、三进程描述方式

三进程描述方式是指在VHDL语言程序的结构体中,使用三个进程语句来描述有限状态机的功能:一个进程用来描述有限状态机中的次态逻辑;一个进程用来描述有限状态机中的状态寄存器;另外一个进程用来描述有限状态机中的输出逻辑。

2、双进程描述方式

双进程描述方式是指在VHDL语言程序的结构体中,使用两个进程语句来描述有限状态机的功能:一个进程语句用来描述有限状态机中次态逻辑、状态寄存器和输出逻辑中的任何两个;另外一个进程则用来描述有限状态机剩余的功能。

3、单进程描述方式

单进程描述方式是指在VHDL语言程序的结构体中,使用一个进程语句来描述有限状态机中的次态逻辑、状态寄存器和输出逻辑。

1、硬件应用

在数字电路中,FSM 可以用可编程逻辑设备、可编程逻辑控制器、逻辑门和触发器或继电器来建造。更明确的说,硬件实现要求寄存器来存储状态变量,确定状态转移的一块组合逻辑,和确定 FSM 输出的另一块组合逻辑。一类经典硬件实现是 Richard控制器。

2、软件应用

下列概念经常用来建造有有限状态机的软件应用:

●事件驱动 FSM

●虚拟 FSM (VFSM)

●基于自动机编程