0

0

电子产业一站式服务平台

电子百科

环境温度:+5~+55℃

安装位置:外壳上箭头与水流方向一致,控制器前须要有10D(管径)长度的导向直管道。

安装管道:1-6"

设定值范围:20-2000升/分

耐压:2MPa

触点容量:AC 250V 3A(阻性)

寿命:1×105次

介质温度:5~80℃

ATM异步传递方式是建立在电路交换和分组交换基础上的一种面向连接的快速分组交换技术,它采用定长分组作为传输和交换的单位,并具有端到端QOS保证、完善的流量控制和拥塞控制,以及较好的技术综合能力等优势,这些都是目前的IP技术所不及的。和传统的STM电路相比,ATM技术对数据交换中猝发分组的适应能力和传输线路的利用率都是很高的。虽然,由于灵活性和价格的原因,ATM技术没有获得预期的成功,但其流量控制机制对当前变长分组骨干网的流量控制还是具有重要的参考价值,所以有必要对ATM的流量控制及其实现方式进行深入的研究。

IP核是一段具有特定电路功能的硬件描述语言代码,该程序与集成电路工艺无关,因而可以移植到不同的半导体工艺中去生产集成电路芯片。随着CPLD/FPGA的规模越来越大,设计越来越复杂,使用IP核是一个趋势。

本文研究了ATM流量控制的原理,并给出了一种IP核的实现方法,该IP核不仅可以用于独立芯片,还可以作为系统的一个子模块直接调用。

1ATM流量特性分析

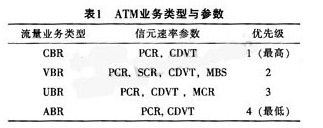

由于ATM支持的业务范围很广,各种业务对网络传输的要求也大不相同,所以需要对不同的业务进行管理。当用户建立连接时都必须与网络达成一个合约,并在通信过程中要受该合约的约束,同时网络按合约提供相应的服务,具体的业务特性参数描述如下:

(1)峰值信元速率(PCR)表示用户可以发送信元的最大瞬时速率;

(2)持续信元速率(SCR)表示一段时间内的平均信元速率。但SCR并不是任意一段时间内的平均信元速率。它是一个ATM连接上的平均信元速率的上限值;

(3)最大突发长度(MBS)指的是以峰值信元速率能够连续发送的最大信元数目;

(4)最小信元速率(MCR)则是用户可接受的最小信元传送速率。

而后,ATM论坛又按照用户要求的比特率特点将业务划分为以下几种主要的类型:

(1)恒定比特率(CBR)

用户要求固定带宽的连接,带宽大小由PCR说明。该类服务对CDVT有严格要求,适用于实时应用,如话音和视频信号传输等。

(2)变比特率(VBR)

在连接期间的带宽要求随时间变化,其带宽值用PCR、SCR、MBS表征,适用于突发的数据传输。

(3)不指明比特率(UBR)

支持非实时业务,如文件传送和电子邮件。UBR用PCR来表征,但网络只是以"最大努力"来传送这类业务。

(4)可用比特率(ABR)

ABR不适用于实时应用,但它要求保持较低的信元丢失率。当连接建立时,系统将以PCR和MCR分别指明最大需求带宽和最小可用带宽。而当连接建立后,系统则将根据网络当前负载情况的反馈信息来调整发送速率,但不能小于MCR。该类常用于信令的传输。具体的流量类型和参数见表1所列。

2ATM流量控制器的原理和设计

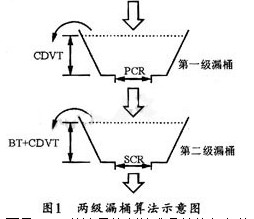

实际应用中最常见的两种业务模式是CBR和VBR,它们分别对应着当前通信传输的语音和数据业务。针对ATM的流量算法为GCRA(一般信元速率算法)。该算法可采用公式GCRA(I,L)来描述。其中I是时间增量,表示相对当前时刻的下一个信元到达时间间隔的理论值(期望值)。L是信元时延偏差容限,表示相对期望值的下一信元可以提前到达的最大容忍范围。对应于双漏桶算法,它可以表示为第一级漏桶处理PCR,相应模型为GCRA1(1/PCR,CDVT)。第二级漏桶处理SCR的相应模型为GCRA2(1/SCR,BT+CDVT),根据ATM论坛规定,PCR是必须的,而SCR是可选的。如果其中的L的值较大,则将增大数据的突发程度。第一级漏桶的监控是针对单个信元的,经过第一级漏桶的平均速率可以得到控制,但是突发性还是没有得到控制。第二级漏桶是以监控若干个信元为目的,它对突发性有良好的监控和抑制作用。对于CBR型的流量,只需要第一级漏桶,因为它没有数据突发的概念,而对于VBR业务类型,第二级漏桶也是需要的,因为它有数据突发可能,所以要对它进行监控。其两级漏桶算法的示意图如图1所示。

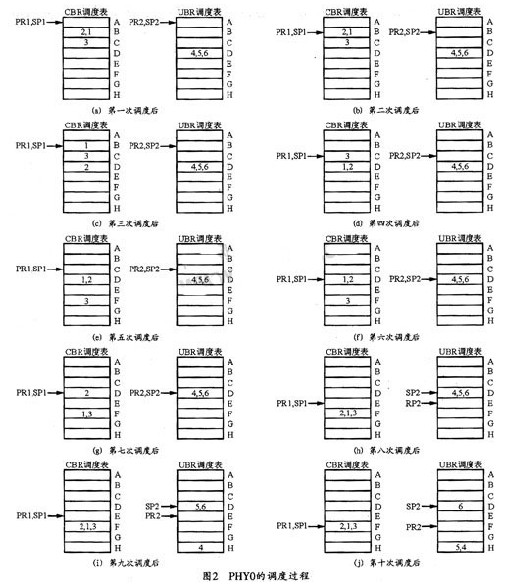

由此可见,ATM的流量控制技术是较为复杂的,而且也是其精髓之所在。在参考各种资料的基础上,本文提出了一种流控的调度算法。这种调度算法是基于各个UTOPIA的PHY接口实现的。每个PHY的接口上可能存在多种流量类型(如CBR,VBR等)。该算法可根据每个PHY的流量类型来设置相应的多个调度表,每个表代表一种流量类型(如CBR,VBR等)。每个表由多个时隙槽组成,每个时隙槽中有多个要请求发送的ATM连接,每个时隙槽中的连接容量定义为cell per slot(CPS)。每个表由两个指针组成,分别为实时指针RP和服务指针SP,其中RP在每经过CPS个CELL发送时间后将移动到下一个时隙槽,而SP则要等到某个时隙槽没有等待发送的CELL时才能往下移动。如果一个连接在本时隙槽发送完后接着被调度到下个时隙槽发送,那么,此时将达到连接的最大比特速率为:

链接的最大速率=PHY端口的线速/CPS

同理,某连接的最小速率就表示在每次表的轮询过程中只被调度一次,其可以表示为:

最小比特速率=PHY端口的线速/((时隙数-1)×CPS)

假设PHY0的调度表的初始状态如图2左上角的图形所示,其中CPS=2,有8个时隙(timeslot),PHY0共有两个流量类型,那么,将有两个优先级的调度表,分别是CBR和UBR业务类型,显然CBR业务类型的优先级高于UBR。调度表中的空白表示该时隙没有连接,连接1、2被安排在时隙B发送,连接3在时隙C,连接4、5、6在时隙D。CBR和UBR都是PCR通信类型,它们可根据参数PCR来进行调度。对于连接1、2,PCR=1/2MaxPCR;对于连接3,PCR=1/3MaxPCR;对于连接4、5、6,PCR=1/4MaxPCR。开始时,服务指针和实时指针都指向时隙A。从图2可以看到PHY0的整个调度过程。第一次调度时,两个调度表的当前时隙(时隙A)均没有CELL;第二次调度时,调度表中仍没有连接,实时指针指向下一个时隙(时隙B);第三次调度时,CBR调度表的时隙B中有连接2和1,先调度2发送,然后为连接2重新安排调度,由于连接2的PCR=1/2MaxPCR,所以将2写入时隙D;

第四次调度时,连接1的处理类似;第五次调度时,调度连接3,其下次调度安排在时隙F;第六次调度时。CBR和UBR调度表的当前时隙(时隙C)中都没有连接,实时指针指向时隙D;第七次调度时,CBR和UBR调度表的时隙D中均有连接,由于CBR优先级高.故从CBR调度表中读取连接1;第八次调度时,连接2被调度,实时指针指向时隙E,注意到此时由于UBR的连接未被调度,所以SP的指针就指在了那里:第九次调度时,CBR调度表的时隙E中没有连接,而UBR的时隙D有3个连接要求调度,这时从UBR调度表中调度连接4,调度完后根据流量参数将连接4写入时隙H;第十次调度时,调度连接5,然后将连接5写入时隙H同时实时指针下移,但是,因为还有连接6没有被调度,所以服务指针还在D处。其余的调度可以以此类推。

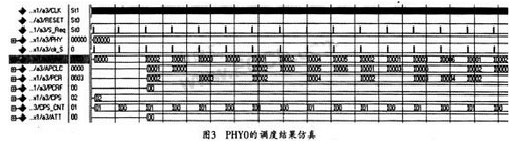

3功能仿真及验证

该ATM流量控制器可采用硬件描述语言Verilog HDL进行描述。图3所示是在ModelSim软件环境中进行功能仿真的相应仿真结果。

在图3所示的PHY0调度功能仿真结果中,CLK是工作时钟,reset是复位信号,S[[_]]Req是调度请求信号(S[[_]]Req有效时进行调度),clr[[_]]S是调度请求清除信号,PHY是选中的物理设备的地址(即要进行调度的物理设备地址),chn是调度到的ATM的连接号。APCLC是当前调度到的连接所连接的下一个连接号,PCR是峰值信元速率对应的时隙调度速率,CPS是每个时隙发送的信元数,CPS[[_]]CNT是信元计数,ATY是ATM通信类型指示(00表示PCR通信类型)。本设计中的CBR和UBR都是PCR通信类型,所以ATT均为00。从仿真结果可以看出,调度到的连接号依次为0、0、2、1、3、0、1、2、4、5、2、1、3、6、1、2…,可见,与上面调度算法的分析结果一致。

4结束语

本文主要研究了在FPGA上利用VerilogHDL实现ATM流量控制的方法,提出了一种较为实用的算法机制,并在此基础上给出了对应的IP核设计。通过对其进行的功能仿真结果表明,该算法运行良好且高效,可以满足实际系统的需要。