0

0

电子产业一站式服务平台

电子百科

新唐科技的NUC1xx包含NUC101、NUC100、NUC120、NUC130和NUC140,是以ARM Cortex-M0为核心的32位微控制器(MCU),经由不同时钟的设定,最高可以达到50MHz的运作频率。然而在一般简单控制或系统负载较低时,CPU并不需要执行在最高的运行时钟下即可应付所需要的计算量。这时候,便可以利用系统时钟的控制来降低时钟,以达到省电的目的。

另一种情况是CPU因为等待下一个工作或只需要久久工作一次时,就可以先将CPU进入Idle或Power Down模式,等到一定的时间之后或是有特定的事件发生时,才被唤醒过来进行相关事件的处理。同时,如果系统内没有用到的系统模块,也可以将其关闭以节省不必要的耗电。本文介绍各种不同的省电方法的原理,并提供相关的范例说明。

开关系统模块

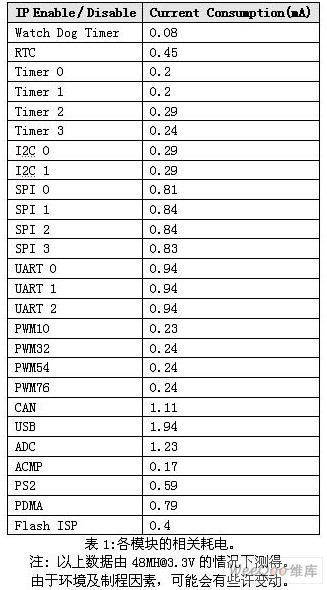

在新唐科技NUC1xx中,为了省电的需求,当某个系统模块不使用时,可以将其输入时钟关闭,使其进入关闭的模式,依此来达到省电的效果。在NUC1xx中,几乎所有的系统模块都可以各别被关闭,这些模块包括:Watch Dog Timer、RTC、Timer0~3、I2C0~1、SPI0~3、UART0~2、PWM0~7、CAN、USB、ADC、ACMP、PS2、PDMA、 Flash ISP。不过,并非每颗芯片都包含了所有模块功能,例如CAN模块只在NUC130和NUC140才有此功能,详细说明请参考各芯片的相关文件。

各模块的相关耗电如表1所示。

新唐科技NUC1xx藉由关闭各模块时钟的方式来达到关闭各模块的目的,所以要关闭模块就必须设定相关的时钟控制缓存器。NUX1xx提供AHBCLK Register与APBCLK Register,来控制上文所列出各模块的开关。

系统时钟设定

新唐科技NUC1xx本身的耗电量和它的运行时钟有很大关系。如果运行的时钟高,则耗电高,反之则比较省电,但同时CPU就可能无法负荷大量的运算。因此,如果要同时兼顾大量运算跟省电,就必须能够根据实际上的需求来调整CPU的工作时钟,以求达到最佳的运作效率。

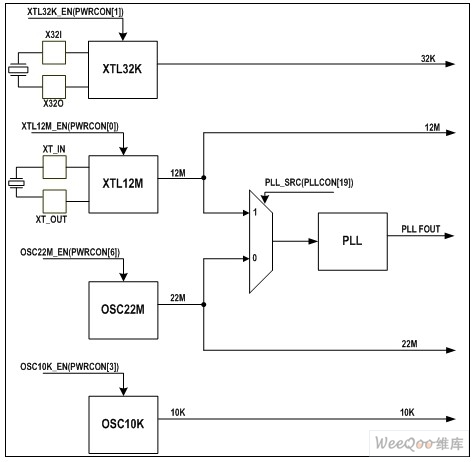

NUC1xx内建了PLL,能使用外部12MHz的晶振或是内部22M振荡器产生系统所需的时钟,由PLL所产生的时钟再经过适当除频,即可作为CPU的工作频率。另外NUC1xx也提供经由外部32KHz的晶振或是内部10KHz 振荡器直接供给作为CPU工作频率的方式。因此,NUC1xx对于工作时钟的设定,提供了很大的灵活性。

IDLE省电模式

新唐科技NUC1xx除了可利用设定最适合的工作时钟来达到省电的目的外,如果在系统完全不需要工作时,还可以将CPU及大部分的硬件关闭,以达到最大的省电效果。这种搭配关闭CPU及大部分硬件的模式,我们称之为省电模式,其中包括了Idle省电模式及Power Down省电模式。下面就Idle省电模式进行说明。

藉由关闭大部分硬件时钟以达到最大省电效率的模式主要有两种,一种是Idle省电模式,另一种是Power Down省电模式。这两种模式最大的不同点是,当系统进入Idle省电模式下时,任何的中断事件都可以重新唤醒CPU,以便让系统可以处理新进的事件。但如果系统处于Power Down省电模式,就只有少数特定的中断事件能够唤醒系统。

由于所谓的Idle模式,实际上就是把CPU的时钟关闭,这样让CPU在没有工作时处在最省电的模式。因为在这个模式下,只是将CPU的时钟关闭,一旦有任何中断事件发生,马上可以打开CPU的时钟来处理相关的事件,所以不会造成处理事件的延迟,同时又可以达到省电效果,是兼顾速度与省电的一种模式。

NUC1xx可以利用ARM Cortex-M0本身提供的WFI/WFE指令进入Idle模式。一旦进入Idle模式,CPU将立刻进入Sleep模式而停止运作,因此在WFI/WFE指令之后的程序都必须等到CPU被唤醒后才会被执行。此时NUC1xx的耗电量将降到约16mA@3.3V-48MHz。

进入Idle省电模式之后,如果要唤醒CPU,回到一般的工作模式,就必须先产生中断信号。该中断信号可以是NUC1xx中的任何模块所产生的中断,也可以通过外部中断的方式来唤醒CPU。需要注意的是,当决定CPU要由某个中断来唤醒时,就必须在进入Idle省电模式前,将该中断设定完成,才能使其产生中断事件来唤醒CPU。

Power Down省电模式

Power Down是新唐科技NUC1xx最省电的一种模式,因为一旦进入Power Down省电模式,晶振时钟会被关闭,整颗NUC1xx呈现静止的状态,这时的耗电量将减到最小的程度。而在此模式下,也只有少数的特定中断事件能够唤醒NUC1xx,使其恢复工作状态。在Power Down模式下,NUC1xx提供了GPIO、USB、UART、RTC、ACMP和CAN的中断唤醒方式。

要进入Power Down省电模式,除了必须呼叫WFI/WFE指令外,在调用WFI/WFE指令之前,必须另将PD[_]WAIT[_]CPU和PWR[_]DOWN[_]EN两个功能依序打开。已确保CPU先进入Sleep模式后,系统再进入Power Down模式,此时NUc1xx是属于最省电的状态,耗电量将降到约15uA。

一旦NUC1xx进入Power Down省电模式,由于大部分的逻辑电路都进入停止状态,因此要想唤醒CPU,必须经由特殊定义的中断源来唤醒。在Idle省电模式下,只要有任何中断即可唤醒CPU不同,不过相同的是,两者都必须要在进入省电模式前,先设定好将来要用来唤醒CPU的模块,这包括其中断或唤醒功能,这些为了唤醒CPU的准备都完成之后,才能进入省电模式,否则就没有任何方式能够再唤醒CPU了。

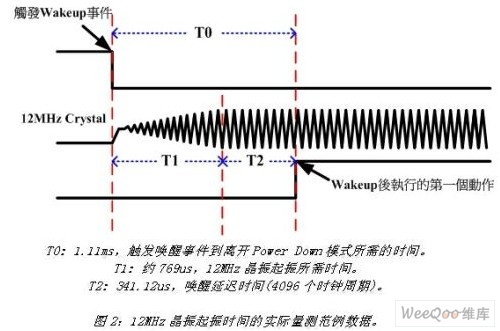

由于所谓的Power Down省电模式,实际上是把晶振的时钟关闭,让整个NUC1xx呈现静止的状态。而因为晶振也被关闭了,一旦有唤醒中断事件发生,需要等到晶振稳定下来后,CPU才能继续运作,所以由Power Down进入一般的工作模式,会需要延迟一点时间来等待,而NUC1xx系列所提供的延迟时间预设为4096个clock cycle。以12MHz来计算,延迟时间为(1/12MHz)*4096=341.12us(图2中的T2),而晶振起振所需时间(图2中的T1)则会随着晶振频率、品牌、PCB 布线等都会造成少许差异。一般而言, 12MHz晶振起振所需时间约1~2ms。实际量测范例数据如图2所示。

本文小结

本文介绍了新唐科技NUC1xx所提供的各种省电方式,包括了关闭没用到的模块、调整CPU运作的时钟、Idle省电模式与Power Down省电模式。在实际应用时,使用者可以根据自身所需,选择适合的方式,甚至组合不同的省电方法以达到最佳的省电效率。

这样的区别主要集中在硬件结构、应用领域和指令集特征3个方面:

1)硬件结构

微处理器是一个单芯片CPU,而微控制器则在一块集成电路芯片中集成了CPU和其他电路,构成了一个完整的微型计算机系统。图1-6虚线框中所示是大多数微控制器的完整结构。除了CPU,微控制器还包括RAM、ROM、一个串行接口、一个并行接口,计时器和中断调度电路。这些都集成在一块集成电路上。虽然片上RAM的容量比普通微型计算机系统还要小,但是这并未限制微控制器的使用。在后面可以了解到,微控制器的应用范围非常广泛。

微控制器的一个重要的特征是内建的中断系统。作为面向控制的设备,微控制器经常要实时响应外界的激励(中断)。微控制器必须执行快速上下文切换,挂起一个进程去执行另一个进程以响应一个“事件”。例如,打开微波炉的门就是一个事件,在基于微控制器的产品中这个事件将触发一个中断。微处理器也能拥有强大的中断功能,但是通常需要外部元件的配合,而微控制器在片上集成了所有处理中断必需的电路。

2)应用领域

微处理器通常作为微型计算机系统中的CPU使用。其设计正是针对这样的应用,这也是微处理器的优势所在。然而,微控制器通常用于面向控制的应用。其系统设计追求小型化,尽可能减少元器件数量。在过去,这些应用通常需要用数十个甚至数百个数字集成电路来实现。使用微控制器可以减少元器件的使用数量,只需一个微控制器、少量的外部元件和存储在ROM中的控制程序就能够实现同样的功能。微控制器适用于那些以极少的元件实现对输入/输出设备进行控制的场合,而微处理器适用于计算机系统中进行信息处理。

3)指令集特征

由于应用场合不同,微控制器和微处理器的指令集也有所不同。微处理器的指令集增强了处理功能,使其拥有强大的寻址模式和适于操作大规模数据的指令。微处理器的指令可以对半字节、字节、字,甚至双字进行操作。通过使用地址指针和地址偏移,微处理器提供了可以访问大批数据的寻址模式。自增和自减模式使得以字节、字或双字为单位访问数据变得非常容易。另外,微处理器还具有其他的特点,如用户程序中无法使用特权指 令等。

微控制器的指令集适用于输入/输出控制。许多输入/输出的接口是单/位的。例如,电磁铁控制着马达的开关,而电磁铁由一个1位的输出端口控制。微控制器具有设置和清除单位的指令,也能执行其他面向位的操作,如对“位”进行逻辑与、或和异或的运算,根据标志位跳转等。很少有微处理器具备这些强大的位操作能力,因为设计者在设计微处理器时,仅考虑以字节或更大的单位来操作数据。

在对设备的控制和监视方面(可能是通过一个1位的接口),微控制器具有专门的内部电路和指令用于输入/输出、计时和外部中断的优先权分配。微处理器一般需要配合附加的电路(串行接口芯片、中断控制器、定时器等)才能执行相同的任务。不过,单纯就处理能力而言,微控制器永远达不到微处理器的水平(在其他条件相同的情况下),因为微控制器芯片中的集成电路的很大一部分用于实现其他的片上功能,代价就是牺牲掉一部分处理能力。

由于微控制器芯片上的资源非常紧张,它的指令必须非常精简,大部分指令的长度都短于1个字节。控制程序的设计原则通常是要求程序能够装入片上的ROM,因为即使只增加1片外部ROM也将显着提高产品的硬件成本。微控制器指令集的基本特点就是具有精简的编码方案。微处理器不具备这样的特点,因为它们强大的寻址模式使得指令编码不够简洁。

引言

随着我国航天事业的发展,高密度集成电路器件在航天器的研制中被大量使用,然而随着器件集成度的提高和工作电压的降低,空间辐射环境对电子系统的影响越来越多。空间辐射环境对电子系统的损害最主要的是单粒子效应(Single Event Effect) ,它们会使器件失效或者工作状态发生改变,影响电子设备的可靠运行 5。基于笔者所在单位承担的大量航天工程任务中关键部位均使用了 8051微控制器,本文根据航天电子设计的要求对一款8051IP软核进行了修改,以适应航天设备的需要。

1 mc8051IP核介绍

IP(Intellectual Property)原意指知识产权,在 IC设计领域则是指预先设计实现某种功能的模块。IP核(IP模块)则是指完成某种功能的虚拟电路模块,也称之为虚拟部件。

根据 IP的提供方式通常把 IP核分为硬 IP(硬核 Hard Core)、软 IP(软核 Soft Core)和固 IP(固核 Firm Core )。

硬核是针对某个特定工艺的一套物理版图,电路布局布线和工艺是确定的,已经过样品电路的验证。硬核的优点是它的高速度和安全性,但由于依赖特定的工艺,所以缺少灵活性。

软核是用硬件描述语言(Verilog HDL或 VHDL)的形式描述功能块的行为,但是并不涉及用什么电路和电路元件实现这些行为。软核具有的特点是可以根据用户需要灵活的进行修改定制。

固核是一种介于软核和硬核之间的 IP核,通常以 RTL代码和对应具体工程网表的混合形式提供。固核是完成了综合的功能块,有较大的设计深度,通常以网表的形式提交客户。

mc8051IPcore是 Oreganosystems公司提供的一个应用广泛的开源 8051IP软核。

它由算术运算单元,定时器 /计数器,串口,内部 ram,外部 ram及 rom组成。mc8051[_]alu为运算单元,由加法器,乘法器,除法器等基本运算单元组成。mc8051[_]control为 mc8051的控制通路。包括有特殊寄存器,译码单元,多路选择器,中断及指令状态机等基本功能。2抗单粒子可靠性设计技术

可靠性设计的基本原理是冗余,包括信息冗余,时间冗余等。目前抗单粒子效应的设计技术中应用最广的技术有三模冗余(Triple Modular Redundance ,TMR),检错纠错(Error Detection And Correction ,EDAC) 1基于软件的控制流检测

2。本文主要采用前2种可靠性设计方法。

2.1 三模冗余(TMR)介绍

三模冗余是指将目标部件复制相成同的三个目标部件来实现一个目标部件的功能,三个目标部件最终将通过一个判决器来判断目标部件的正确状态。它利用的是相同一组部件同时出现错误概率较小的原理来实现可靠性的提高。

TMR可用于各种IP设计的各阶段,既可以在系统级进行冗余,也可以是局部冗余。

2.2 纠错检错(EDAC)

2.2.1 EDAC概述

EDAC可以用来检测电子设备中由SEU引起的存储为翻转错误。EDAC的基本结构包括3个部分:编码模块,解码模块,存储模块。其中EDAC编码模块将需要处理的数据进行相关算法的编码,产生校验码,与待处理数据一同存入存储模块。数据需要读出的时候,EDAC解码模块将数据与相应校验码进行解码处理,得出正确结构。编码与解码所采用的编码方式可以根据需要选择,如汉明码,最佳奇权码,藤原英二码等等。

2.2.2 汉明码介绍

下面以扩展汉明码为例说明编码纠错检错的原理。 扩展汉明码(Extended Hamming Code)在存储系统的纠错检错中得到了广泛应用。他的最小码距是4,对于数据位数 k,校验位数 r,他们之间的关系需满足 2r-1 ≥ k+r。如果数据位 k增加一倍,校验位 r也只需要增加1位,所以它具有相当高的编码效率。 8位数据经过4位编码后的数据结构如下:

C= [D7D6D5D4D3D2D1D0C3C2C1C0]其中 D7~D0是数据位,C3~C0是校验位:

C3= D7 ⊕D6 ⊕ D5 ⊕ D4 ; C2= D7 ⊕D3 ⊕ D2 ⊕ D1; C1= D6 ⊕D5 ⊕ D3 ⊕ D2 ⊕ D0 ; C0= D6 ⊕D4 ⊕ D3 ⊕ D1⊕ D0

解码时需计算存储数据的伴随向量 S: S3= C3 ⊕CB3;S2= C2 ⊕CB2 ;S1= C1⊕CB1;S0= C0 ⊕CB0 其中 CB0,CB1,CB2,CB3为 8位数据在解码时刻的校验位。根据算得的伴随向量 S我们就可以判断数据位是否发生错误及错误发生的位置。

2.3 两种纠错方法的比较

TMR与 EDAC都属于硬件冗余,对于不同字长的存储器,他们所占用的面积开销和时间开销是不同的。TMR所占用的面积开销包括冗余的2个目标器件以及判决器及附属电路逻辑,EDAC所增加的面积开销则包括了增加的校验位,编码器,解码器及附属逻辑 1。根据以上分析我们可以得出结论,对于保护寄存器,寄存器组等容量较小的存储器件,TMR有实现简单,增加面积较少的有点。而对于大容量的存储器,则应当采用 EDAC来进行纠错检错。

3高可靠性 8051具体方案设计及实现通过对 SEU的机理分析及 mc8051结构分析可以得出,容易受到粒子辐射的关键部位有

3:特殊寄存器(Special Function Register ,SFR),内部 ram,外部 ram。本论文就上述三个模块对 mc8051IP核进行了该进。

3.1特殊寄存器(SFR)

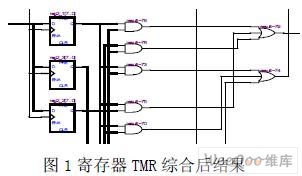

mc8051IP核的特殊寄存器(SFR)均在 control[_]mem文件中实现。该模块实现 8051译码功能。SFR字节地址范围是80H-FFH,他们在 RAM中并不是完全连续的,21个 SFR离散的分布在上述字节区域的128个字节单元中。在mc8051IP核中并没用将这些SFR设计在内部 ram中,而是对应地址分别实现的。对 SFR的加固处理是采用了 TMR技术。具体实现步骤如下:

综合后结果截取如下图:

3.2内部 RAM

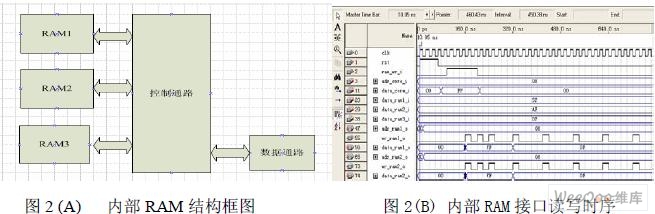

该 IP核可支持 128字节内部RAM.由 2.3分析,方案采用 TMR方式对内部 RAM进行处理,选用 3个相同的 128字节的 RAM作为冗余的存储器,由 mc8051[_]ram[_]fsm与 mc8051[_]ram[_]dataflow两个模块组成了内部 RAM的数据通路,其中前者完成写优先的读写状态控制,后者完成数据流向控制。数据通路负责完成数据校验。控制通路与数据通路组成内部 RAM接口逻辑。经过仿真后内部 RAM接口结构框图及读写时序如下:

图 2(B)可看出:写数据时,数据输入后第二个周期被写入RAM;读数据时,读指令被检测到后的第 5个周期经校验后的正确数据被输出并且被回写给RAM。在接入工程应用时需将外部时钟进行 6倍频以配合 cpu读写时序。

3.3 外部 RAM

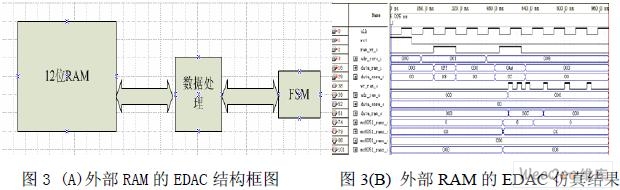

外部 RAM最大可以支持64K,同样由 2.3分析,方案选取能纠 1位错检 2位错的扩展汉明码进行 EDAC处理。其中,数据处理单元完成数据的编码,解码,地址锁存及数据输出功能。读写状态机 FSM完成外部 RAM的读写状态控制,同样,为配合 ram的 IP软核时序,我们将 FSM设计为写优先。仿真后的 EDAC结构框图及读写时序如下:

需要指明的时上图仿真时外部时钟为 10Mhz,经过 altera公司 alt[_]PLL进行了 6倍频及相位调整,前一个写指令未被执行的原因是 PLL需要 2到 3个时钟周期的调整稳定频率输出。 EDAC模块的读写时序与内部 RAM相似,写数据时第 2个时钟周期经过处理后的 8位原数据以及 4位校验数据一同被写进 RAM,读数据时,读出的 12位数据经过解码纠正后在第 5个时钟周期输出 8位数据并将纠正后的 12位数据回写进 RAM,以防止 SEE的积累。由时序图可知以上设计完全符合设计要求。

3.4全系统仿真

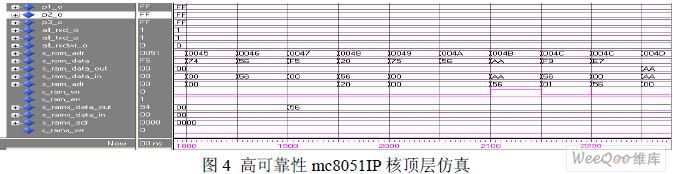

在完成上述几个方面的 IP定修改之后,对 mc8051的顶层系统进行了 modelsim的综合前仿真,仿真部分结果如下:

仿真时将 ROM的初始化文件设置为 mc8051文档中的 tc1.hex,方便与原 IP核进行对照。为在 modelsim仿真前,我们已将 altera的 altera[_]mf库加入到 modelsim库文件中。在进行功能仿真的时候调用了其中的 alt[_]pll来进行时钟处理。在使用该 IP核时可以根据具体采用的器件来完成倍频的功能。以上时序完全正确,说明修改后的 IP核与原 IP核功能上等同。

4结论

本文在oreganosystems公司提供的开源mc8051IP软核的基础上根据高可靠性航天电子设计的方法修改了部分模块,实践证明修改后的功能与原 mc8051IP核完全相同,达到设计目的。可以根据需要将 IP核综合后生成的网表文件下载进现场可编程逻辑器件( FPGA)或者进行流片设计成 ASIC,具备航天使用价值。本文创新点:本文根据在研航天项目需要,定制了一种可适应航天工作环境的微控制器 IP核。采用常用的容错技术对普通商用 IP核进行了加固。该 IP核的成功改造,可以一定程度上减轻我国军品级芯片对国外的依赖,提高了效率,为后续的研究积累了宝贵经验。

1971年英特尔公司三位象爱迪生一样入选美国国家发明荣誉展厅的发明家霍夫、麦卓尔和费根发明了微处理器,霍夫是其中的灵活人物。

1969年英特尔公司承接了日本商业通讯公司要求设计的一款计算器芯片,客户提出至少要用12个芯片来组装机器。8月下旬的一个周末,霍夫在海滩游泳时突然产生了灵感,他认为完全可以将中央处理单元(CPU)电路集成在一块芯片上。

诺伊斯和摩尔支持他的想法,安排逻辑结构专家麦卓尔和芯片设计专家费根设计图纸。1971年1月以霍夫为首的研制小组,完成了世界上第一个微处理器芯片。在3×4毫米的面积上集成了2250个晶体管,每秒运算速度达6万次。它意味着电脑CPU已经缩微成一块集成电路,即“芯片上的电脑”诞生了。

英特尔公司将第一块微处理器芯片命名为4004,第一个4表示可以一次处理4位数据,第二个4代表它是这类芯片的第4种型号。1971年11月15日英特尔公司经过慎重考虑,决定在《电子新闻》杂志上刊登一则广告,向全世界公布4004微处理器,这一天也演变为微处理器的诞生纪念日。

1972年4月霍夫小组研制出微处理器8008,1975年又推出了有史以来最成功的8位微处理器8080。8080集成了约4800个晶体管,每秒执行29万条指令。8080型微处理器正式投放市场是在1974年,这种芯片及其仿制品后来共卖掉数以百万计,引发了汹涌澎湃的微电脑热潮。

在英特尔公司的带动下,1975年摩托罗拉公司推出了8位微处理器6800。1976年费根在硅谷成立了Zilog公司,同时宣布研制成功8位微处理器Z-80,从此微处理器芯片改变了世界。

八十年代初期Z80开始被引进中国,北京工业大学生产了基于Z80的TP801单板机,清华大学周明德教授编写了配套的《微机原理及其应用》教材,株洲电子研究所与香港金山公司合作推出了CMC-80双板机,Z80在八十年代风靡整个中国大地。

而后以复旦大学计算机系陈章龙和涂时亮教授为核心的开发团队,推出了基于Intel公司MCS-48、MCS-51系列微控制器的仿真器,与此同时在上海发起成立了中国单片机学会。在陈章龙和何立民等教授的推动下,组织编写了一系列单片机应用图书,为发展我国的单片机应用事业不计报酬奔赴各地推广,作为我国单片机应用技术的奠基人,他们当之无愧!

其间江苏启东计算机厂通过购买复旦大学计算机系的成果在全国展开单片机的普及推广和市场营销,全国掀起了一股微机应用热潮,启东人功不可没。

其后Atmel、PHILIPS(现更名为NXP)推出了新一代内置Flash技术80C51系列单片机,各地大学开始纷纷开设单片机原理及其应用课程,加速了我国单片机应用技术的发展。

九十年代全球各大半导体开始陆续进入中国市场,推出了各种性能优异的单片机,其中的佼佼者主要有NXP、TI、Atmel、Microchip等,单片机开始大批量商业化应用各行各业。

由于半导体技术的大发展,以及网络技术的与时俱进,现阶段微处理器开始由8位单片机向32位嵌入式系统技术快速迈进,基于ARM核的CPU芯片成为了主流,嵌入式操作系统成为了常规技术,从此开启了中国嵌入式系统应用事业的新纪元。