0

0

电子产业一站式服务平台

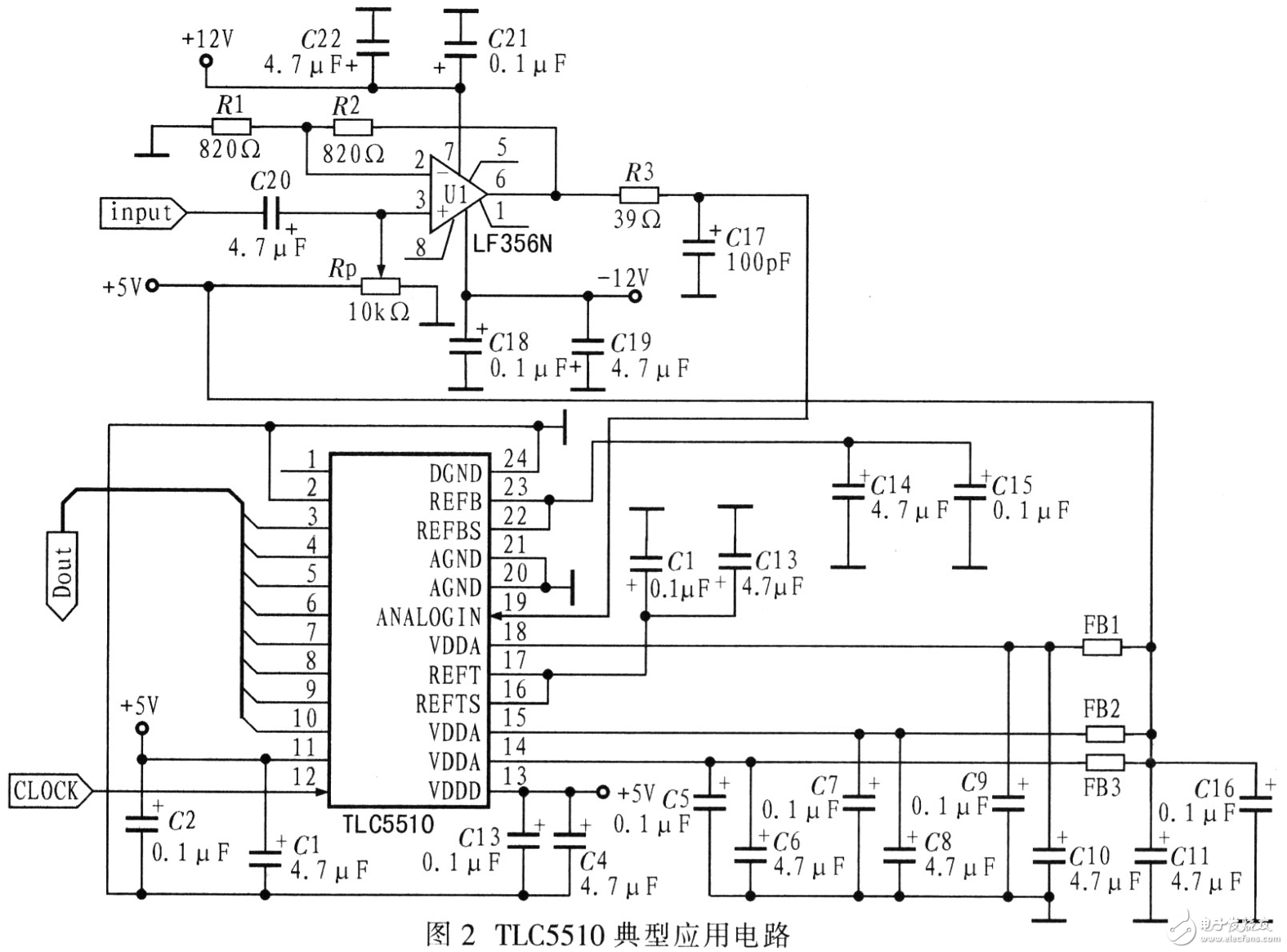

TLC5510的基准电源有多种接法,根据不同场合选择适当基准电源,利用内部基准源,TLC5510典型应用电路如图所示。由于其测量范围为0.6 V~2.6 V(即:TLC5510在转换时模拟输入0.6 V 时对应数字输出00 000 000,2.6 V 对应的数字输出11111 111),因此输入信号在进入TLC5510之前要对其处理,要使该输入信号处于量程内,应加入一个1.6 V的直流分量。

典型应用电路

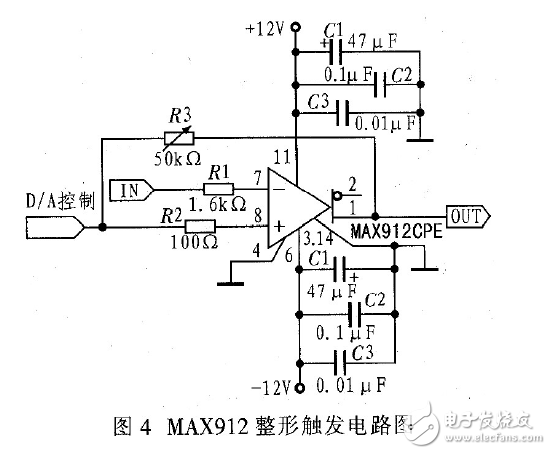

整形触发电路设计

由于每一次采样都要由某一事件触发,所以该系统设计采用内触发,即触发源为被采样信号,并由硬件触发电路实现。该电路可把各种波形的周期信号整形为与原信号周期相同的方波信号。由于采用等效采样技术,其被测信号频率较高。假设被采样信号的最高频率约为10MHz,则整形器件选用电压比较器MAX912。当输入信号电压高于预置的触发电平时,输出高电平;反之输出低电平。图4所示为整形触发电路。

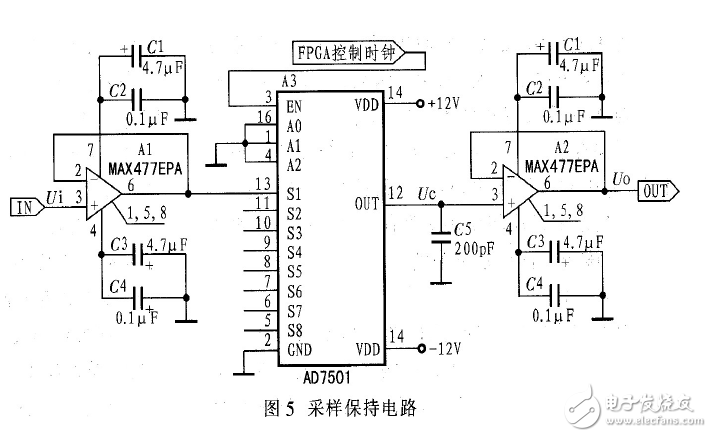

采样保持电路设计

每次采样是比触发时刻延迟N△t 的数据点,但由于被采样信号频率很高,要准确采样到该点基本无法实现。为此需要引入采样保持电路。采样保持电路的功能:在采样时刻到来之前,该模块的输出电压随输入电压变化。当到达采样时刻时,输出电压保持不变。以供TLC5510采样。其具体电路如图5所示。

该采样保持电路由两片运算放大器A1,A2和模拟开关A3构成,采样时通过FPGA 控制时钟使A3的通道S1导通。A1,A2为单位增益的电压跟随器,故Uo=Uc=Uo,此时电容充电至Uc。因电压跟随器的输出电阻很小,故电容快速充电。断开S1,由于Uc 无放电通路,其电压基本不变,故Uo 保持不变, 即保存采样结果。采用传统的实时采样方法可对频率低于1 MHz 的信号进行采样,而对于频率较高的信号,则介绍的基于FPGA 的等效采样技术,能使得TLC5510对高频信号采样,TLC5510应用更加广泛。